@byjr-k

2016-05-31T01:13:09.000000Z

字数 2644

阅读 1938

EEE310 往年试题

大学学习

2014-15

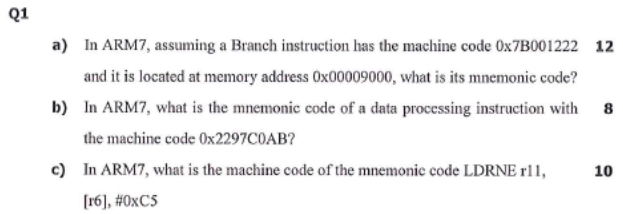

Q1

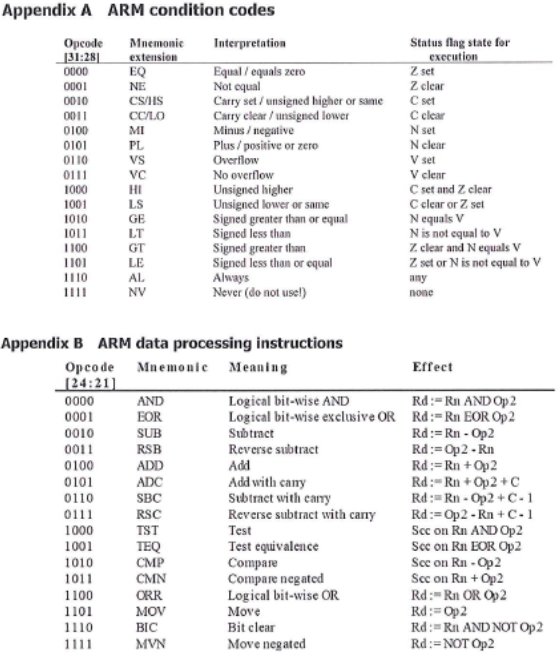

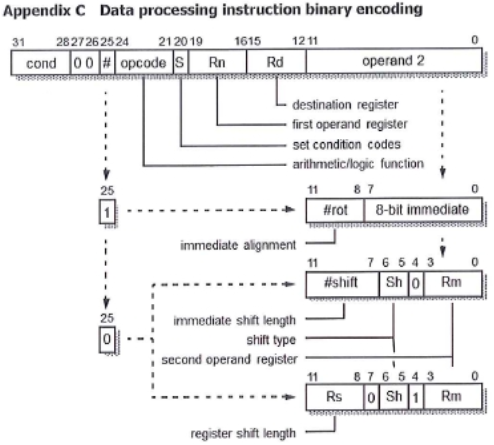

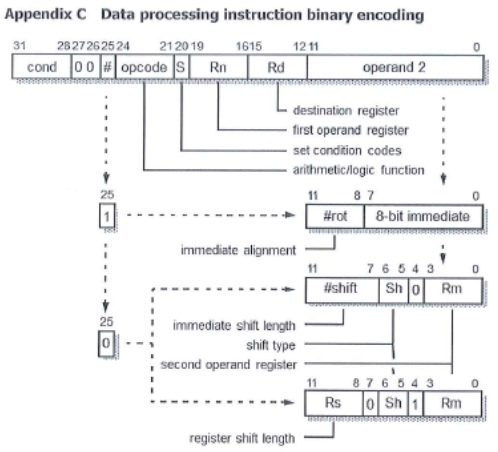

a) Branch instruction 0x7B001222, located at memory address 0x00009000. What is its mnemonic code?

0x7B001222 = 0111 101 1 000000000001001000100010

offset * 4 + 4 + current

00000000 00000000 01001000 10001100

+ 00000000 00000000 10010000 00000000

00000000 00000000 11011000 10001100

D88C

BLVC #0x0000D88C

b) 0x2297C0AB, what is its mnemonic code?

0x2297C0AB = 0010 00 1 0100 1 0111 1100 0000 10101011

cond op S Rn Rd #rot immidiate

ADDCSS r12, r7, #0xAB

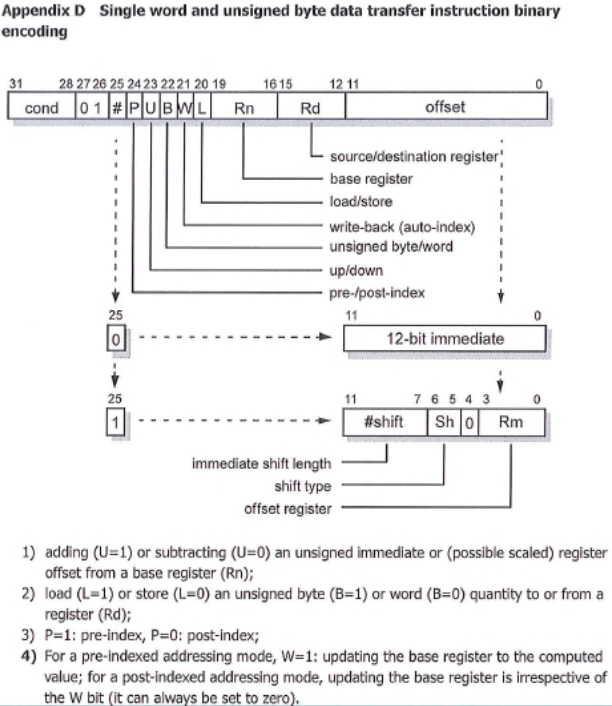

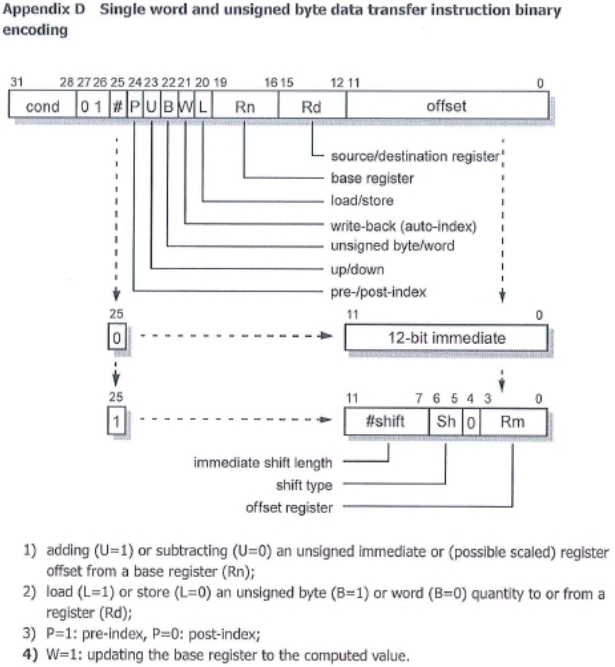

c) LDRNE r11, [r6], #0xC5, what is the machine code?

0001 01 0 0 1 0 0 1 0110 1011 000011000101

cond # P U B W L Rn Rd offset

1496B0C5

如果没有任何对于 flag 的操作,则 cond 是 always 1110

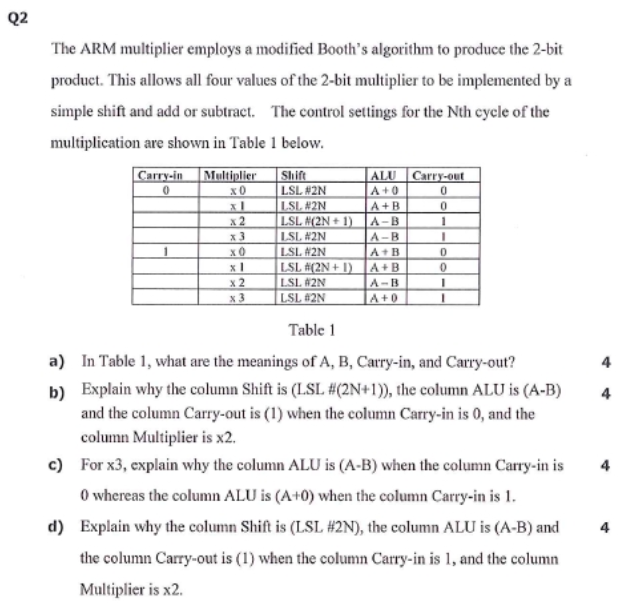

Q2

a) What's the meaning of A, B, Carry-in and Carry-out?

A: running total

B:

Carry-in: the carry value from last calculation

Carry-out: the carry value for the next calculation

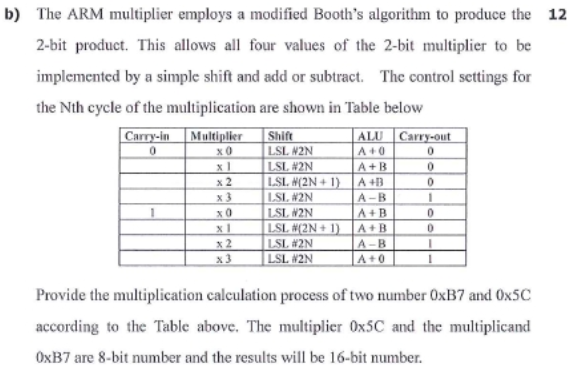

b) 解释 Table 1 第三行

carry-out = 1 -> x4

LSL = #2N+1 -> x2

A - B -> x4 - x2 = x2

c) 解释 Table 1 第四行和倒数第一行

carry-in = 0, Mul = 3 -> x3 + 0 = x3

carry-out = 1 -> x4

LSL = #2N -> x1

A - B -> x4 - x1 = x3

carry-in = 1, Mul = 3 -> x3 + 1 = x4

carry-out = 1 -> x4

LSL = #2N -> x1

A + B -> x4 + 0 = x4

d) 解释 Table 1 倒数第二行

carrr-in = 1, Mul = 2 -> x2 + 1 = x3

carry-out = 1 -> x4

LSL = #2N -> x1

A - B -> x4 - x1 = x3

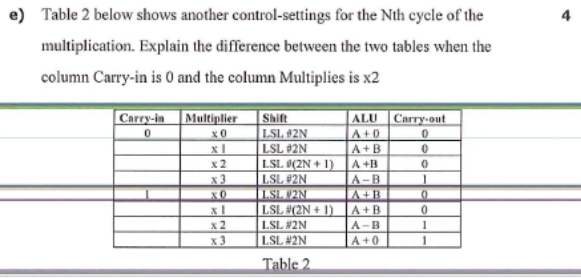

e) 解释两个表的区别

| Carry-in | Multiplier | Table 1 | Table 2 |

|---|---|---|---|

| 0 | 2 | LSL=2N+1(x2), out=1(x4), A-B -> x2 | LSL=2N+1(x2), out=0, A+B -> x2 |

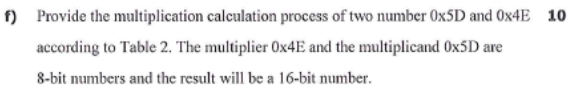

f)

0x5D = 01011101 multiplicand

0x4E = 01001110 multiplier

Table 2:

N in mul LSL ALU out running total

0 0 10 #1 A+B 0 00000000 00000000 00000000 10111010

1 0 11 #2 A-B 1 11111111 11111111 11111110 01000110

2 1 00 #4 A+B 0 00000000 00000000 00000101 00010110

3 0 01 #6 A+B 0 00000000 00000000 00011100 01010110

00011100 01010110 = 1C56

Q3

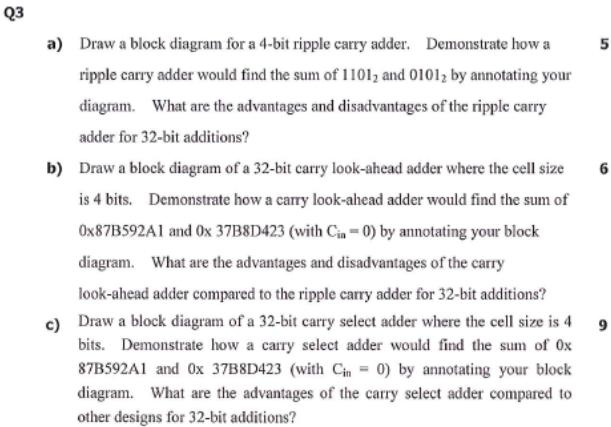

a) 4-bit ripple carry adder

b) 32-bit carry look-ahead adder

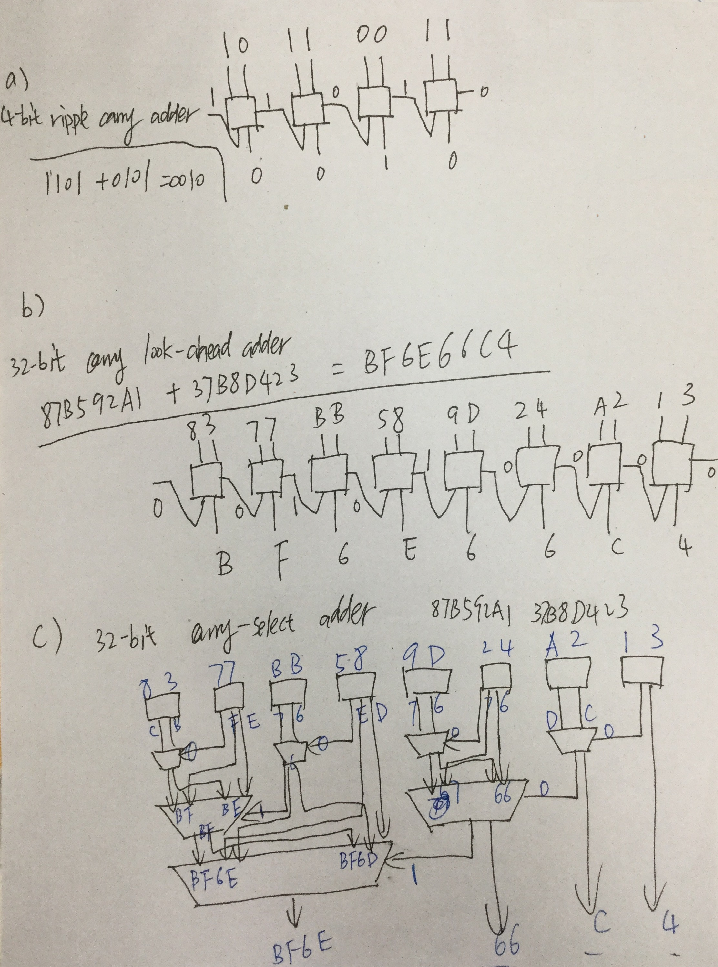

c) 32-bit carry select adder

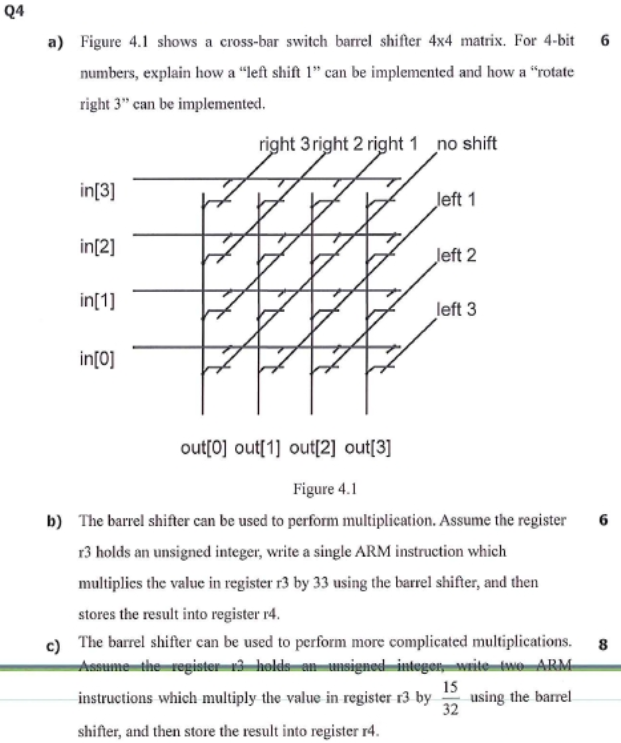

Q4

b)

ADD r4, r3, r3, LSL#5

c)

RSB r3, r3, r3, LSL#4

MOV r4, r3, ASR#5

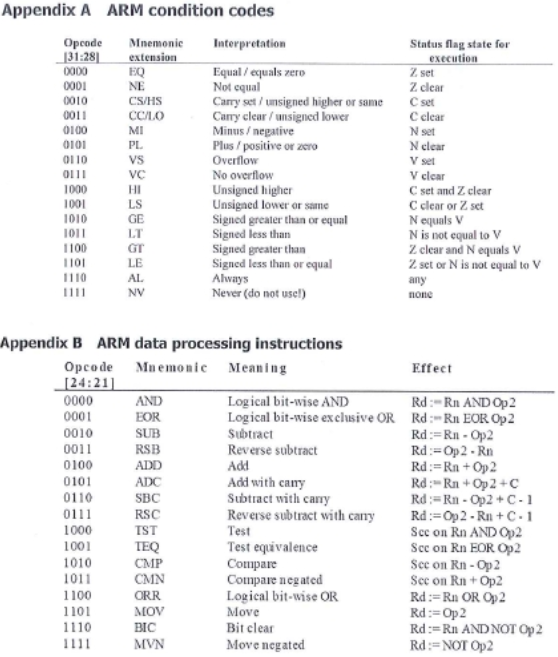

Appendix of 2014-15

2013-14

Q1

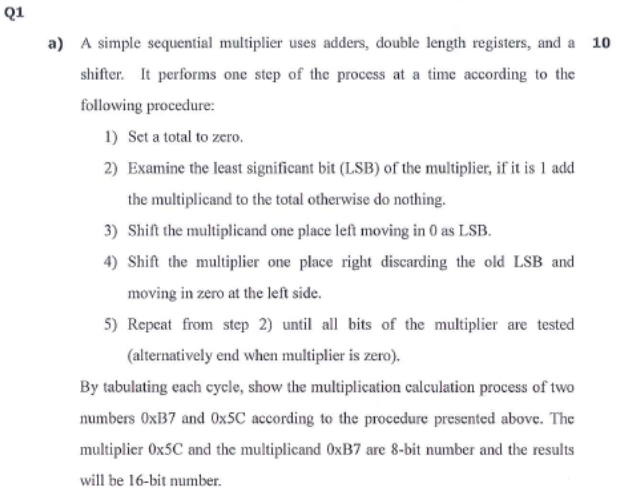

a)

| Multiplier | Multiplicand | total |

|---|---|---|

| - | - | 0 |

| 01011100 | 00000000 10110111 | 00000000 00000000 |

| 00101110 | 00000001 01101110 | 00000000 00000000 |

| 00010111 | 00000010 11011100 | 00000010 11011100 |

| 00001011 | 00000101 10111000 | 00001000 10010100 |

| 00000101 | 00001011 01110000 | 00010100 00000100 |

| 00000010 | 00010110 11100000 | 00010100 00000100 |

| 00000001 | 00101101 11000000 | 01000001 11000100 |

0xB7 = 10110111 = 183

0x5C = 01011100 = 92

0x41C4 = 01000001 11000100 = 16836

b)

Multiplicand = 0xB7 = 10110111

Multiplier = 0x5C = 01011100

| N | in | Mul | LSL | ALU | out | total |

|---|---|---|---|---|---|---|

| 0 | 0 | 00 | 0 | A+0 | 0 | 00000000 00000000 |

| 1 | 0 | 11 | 2 | A-B | 1 | 11111101 00100100 |

| 2 | 1 | 01 | 5 | A+B | 0 | 00010100 00000100 |

| 3 | 0 | 01 | 6 | A+B | 0 | 01000001 11000100 |

01000001 11000100 = 16384 + 256 + 128 + 64 + 4 = 16836

c)

SUB r1, r1, r1, LSL#4

MOV r2, r1, ASR#5

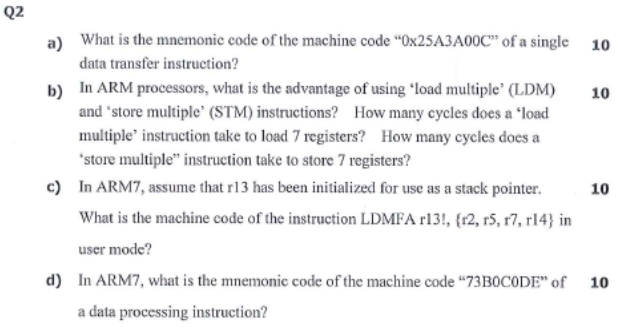

Q2

a) mnemonic code of 0x25A3A00C

0x25A3A00C = 0010 01 0 1 1 0 1 0 0011 1010 000000001100

cond # P U B W L Rn Rd offset

STRCS r10, [r3, #-12]!

b) decrease clock cycle; increase instruction density

LDM 7+2=9

STM 7+1=8

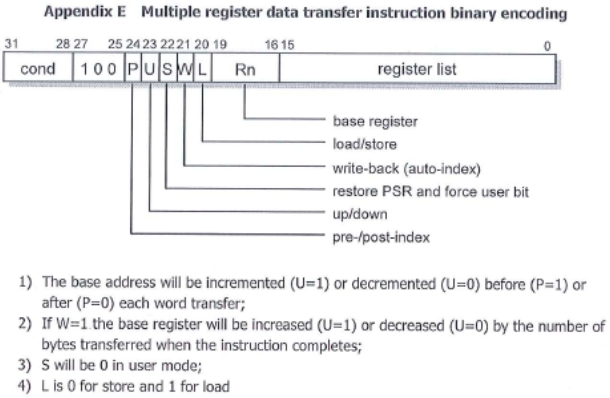

c)

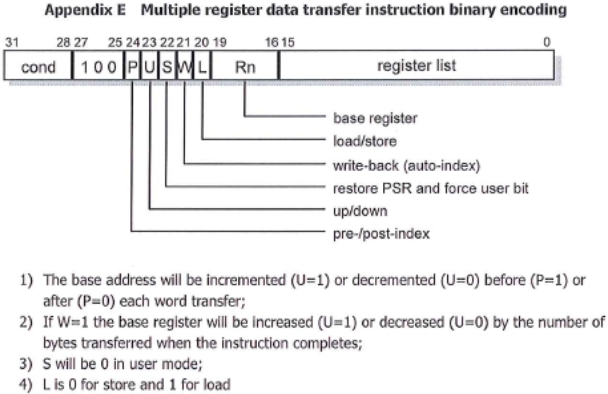

LDMFA r13!, {r2, r5, r7, r14}

1110 100 1 1 0 1 1 1101 0100000010100100

cond 100 P U S W L Rn register list

d)

0x73B0C0DE = 0111 00 1 1101 1 0000 1100 0000 11011110

cond 00 # op S Rn Rd #rot immidiate

MOVVCS r12, r0, #0xDE

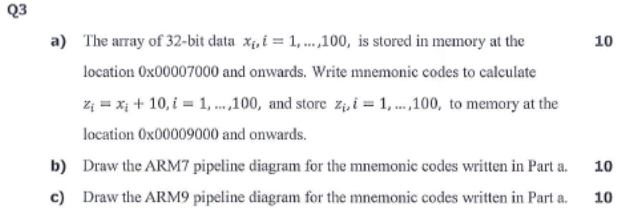

Q3

a)

MOV r1, #0x7000

MOV r2, #0x9000

MOV r3, #100

loop LDR r4, [r1], #4

ADD r4, r4, #10

STR r4, [r2], #4

SUBS r3, r3, #1

BNE loop

b) 3 state

LDR 总共 5 cycle

STR 总共 4 cycle

BNE 总共 3 cycle,需要 E 之后才能开始下一个的 F

c) 5 state

Appendix of 2013-14